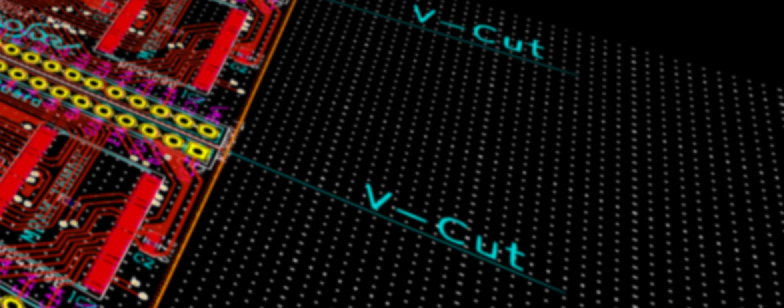

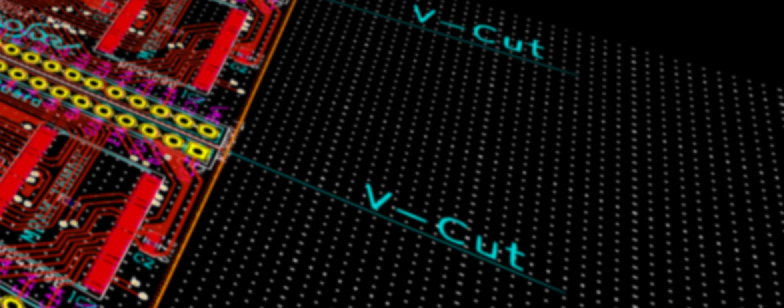

Fusion PCBの基板製造サービス向けの面付データの作りかたをまとめます。以前はシルクレイヤで指示していたV-Cut指示ですが、最近は外形線レイヤにて指示するみたいです。KiCadは外形線にテキスト(シルクテキストの […]

Fusion PCBの基板製造サービス向けの面付データの作りかたをまとめます。以前はシルクレイヤで指示していたV-Cut指示ですが、最近は外形線レイヤにて指示するみたいです。KiCadは外形線にテキスト(シルクテキストの […]

ボードデザインについての資料ページです。 Top-Level Entity Pin Assign Table Pin# Signal-name Direction PIN_6 spi_CS Input PIN_7 spi […]

概要 RAM Cartrish用のメモリ拡張ボードです。最大容量は32MBit(2 Chip)と64MBit(4 Chip)の2種類があります。64MBitはSFCの標準的なアドレスマッピング (Mode25) で扱える […]

RAM Cartrishは5V I/Oに対応したFPGA開発ボードです。FPGA内にロジックを組みあげることで、さまざまな用途に対応する拡張環境が構築できます。もちろん基板単体でもFPGAやマイコンの動作は可能で、各種マ […]

SFC用プログラムを実機または互換機で動作させるためのデバイスです。容量は32kB+32MBit(8kLEモデル)程度のプログラムを保持できます。 現状プロトタイプ段階ですが、生産性(採算)が悪いのでお蔵入り状態です。

細かく言えば、ブラウン管テレビにコンポジットビデオケーブルで接続して表示される、どちらかというとパキパキしていないドット絵が好き。 にじんで汚いとか、ぶちてるとかいう感想は、私は注意を払って使う。 ドット絵製作者の意図 […]